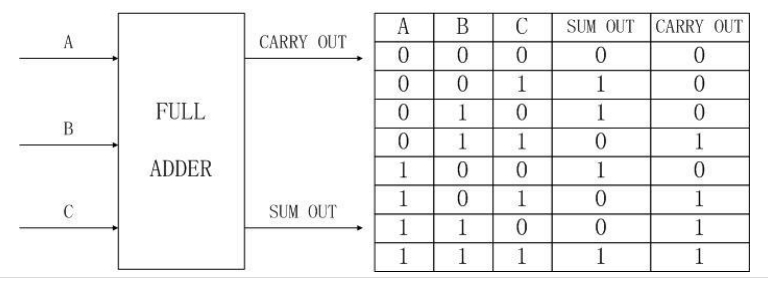

Each full adder carry output is connected as an input carry to the next stage full adder.It consists of 8 full adders which are connected in cascaded form.This is the addition process for 4-bit input sequences when it’s applied to this carry adder.Like this will get the final output sequence (S4 S3 S2 S1) = (1 1 1 1) and Output carry C4 = 0.Here the important point is the second stage full adder gets input carry i.e., C1 which is the output carry of initial stage full adder. Same like for next input bits A2 and B2, output S2 = 1 and C2 = 0.As per this equation, for 1st full adder S1 =1 and Carry output i.e., C1=0.As per its theory, the output equation for the Sum = A1⊕B1⊕Cin and Carry = A1B1⊕B1Cin⊕CinA1 Sum (S1) and carry (C1) will be generated as per the Sum and Carry equations of this adder.When Ao & Bo are applied at 1st full adder along with input carry 0.As per this adder concept, input carry is 0.These are representing the A4 A3 A2 A1 and B4 B3 B2 B1. Let’s take an example of two input sequences 01.4-bit RCA Diagram Working of 4-bit Ripple Carry Adder When this input carry ‘Co’ is applied to the two input sequences A1 A2 A3 A4 and B1 B2 B3 B4 then output represented with S1 S2 S3 S4 and output carry C4. Co is the carry input bit and it is zero always. In this adder, four full adders are connected in cascade. The below diagram represents the 4-bit ripple-carry adder. They are:įirst, we will start with 4-bit ripple-carry-adder and then 8 bit and 16-bit ripple-carry adders. VHDL code for carry look ahead adder can be implemented by first constructing Partial full adder block and port map them to four times and also implementing carry generation block as shown below.There are various types in ripple-carry adders. Partial Full Adder consist of inputs (A, B, Cin) and Outputs (S, P, G) where P is Propagate Output and G is Generate output. Full Adder implementation for Carry Look Ahead Adder

In order to implement Carry Look Ahead Adder, first implement Partial Full Adder and then Carry logic using Propagation and generation Block. It avoid Carry propagation through each adder. For the Purpose of carry Propagation, Carry look Ahead Adder construct Partial Full Adder, Propagation and generation Carry block.

0 kommentar(er)

0 kommentar(er)